随着半导体行业的不断发展,对更高效、可扩展和高性能解决方案的需求正在推动异构集成和先进封装技术的创新。这些创新对于高性能计算、人工智能和边缘计算应用至关重要。这些进步的核心是下一代互连技术的开发,这对于提升性能、增加数据带宽和降低能耗至关重要。

而随着摩尔定律下传统晶体管的微缩已接近物理和经济极限,人们的关注点已转向将各种计算、存储和传感功能集成到紧凑高效的封装中。然而,这种转变的成功在很大程度上取决于先进互连技术的能力,这些技术必须保持高信号完整性、最大限度地降低能耗、提供可扩展性并支持广泛的应用。

互连技术的关键进步包括硅通孔 (TSV)、中介层和混合键合方法的发展。

u 高密度硅通孔 (TSV)(例如间距小于 3 µm 且采用无空隙铜填充)可实现堆叠芯片之间的垂直互连,而 TSV 布局的创新对于降低寄生效应和提升热性能至关重要。

u 中介层和桥接技术也在不断发展,硅中介层用于支持芯片集之间的高带宽连接。有机中介层和玻璃中介层等新兴技术提供了具有独特电气和热性能的经济高效的替代方案。

u 混合键合方法,例如英特尔的嵌入式多芯片互连桥接 (EMIB),无需完整的中介层,从而在提高性能的同时降低成本。

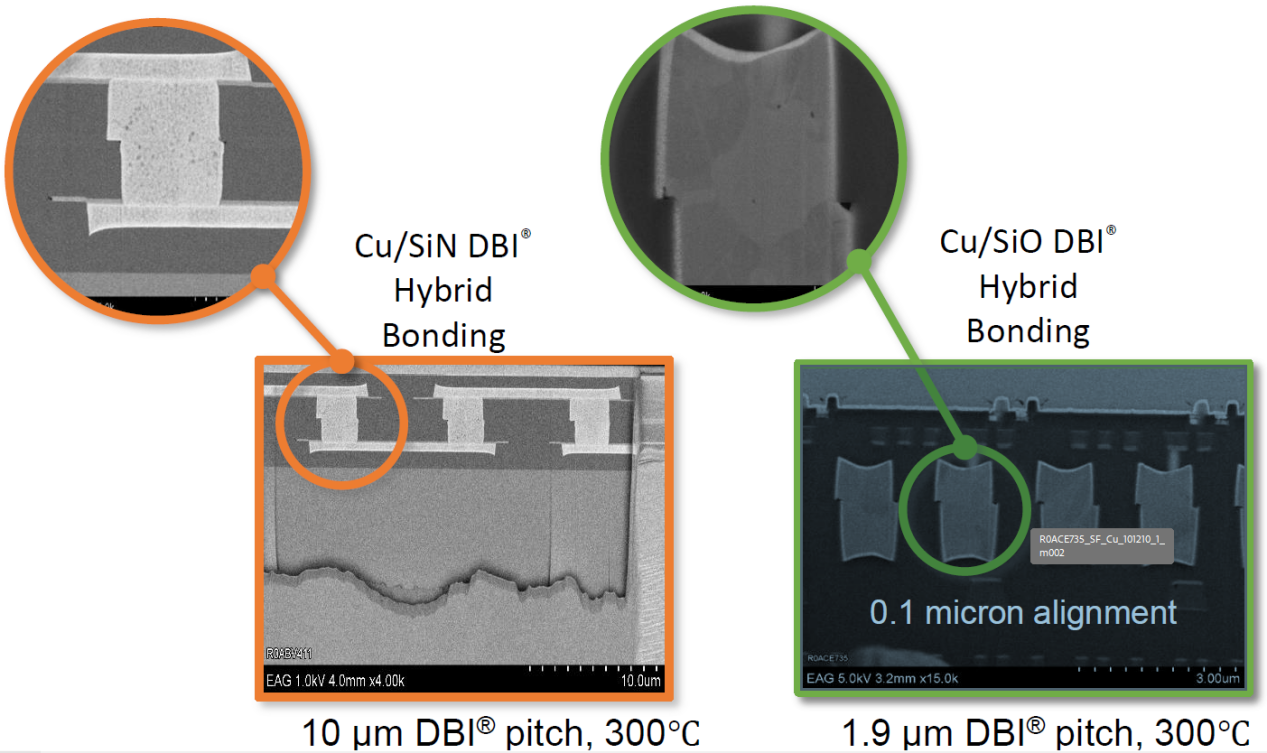

直接键合互连 (DBI:direct bond interconnect) 等混合键合技术也日益受到关注。这些方法通过使用直接电介质键合和金属互连,实现了更高的互连密度和卓越的电气性能。晶圆间键合和芯片间键合技术对于高精度堆叠芯片至关重要,这在需要超高密度和低延迟的应用中尤为重要。下图展示了 10 µm 和 1.9 µm 间距混合互连的示例。

10 µm 间距混合键合(左)和 1.9 µm 间距混合键合(右)

采用先进键合技术实现的混合互连,芯片到晶圆 (C2W) 间距小于 3 µm(互连密度大于 10 5 /mm2),要求:3σ 放置精度小于键合间距的 10%;空隙不得大于键合间距的 0.5%,总空隙密度不超过键合间距的 2.5%;无颗粒和无缺陷(尺寸大于 50 nm)的组装工艺和流程;以及具有无空隙填充(void-free fill)、低应力和弯曲以及高热导率的芯片间间隙填充( inter-die gap fill)材料。

与此同时,人们正在探索光子互连技术,以突破电连接的局限性。片上光子技术可以提供低延迟、高吞吐量的连接,同时功耗更低,使其成为高带宽和长距离通信的理想选择。此外,人们还在开发结合电子和光子互连的混合电光解决方案,以充分利用这两种技术的优势。

重分布层 (RDL) 是先进互连技术的另一个关键组件。用于扇出型晶圆级封装 (FOWLP) 的细间距 RDL 无需硅中介层即可提供高密度连接。双层和多层 RDL 支持更复杂的布线方案,并通过降低电磁干扰来提高信号完整性。将多个异构组件集成在单个封装中的系统级封装 (SoP) 设计也受益于这些进步。高带宽内存 (HBM) 接口依靠先进的互连解决方案在处理单元和堆叠内存之间实现低延迟、高带宽通信,从而实现现代人工智能计算系统中的高效数据传输。

材料和工艺创新对于互连技术的进步至关重要。低损耗、高介电材料的开发可以提高高频信号完整性,而先进的金属化技术则旨在提高可靠性并减少电迁移。铜仍然是标准的互连材料,但人们正在探索钴和钌等替代材料,以实现更小的几何尺寸。有效的热管理解决方案,例如先进的热界面材料和集成散热器,对于高密度互连产生的热量的散热也至关重要。

尽管取得了显著进展,但仍存在一些挑战。随着数据速率的提高,高频信号完整性的管理变得越来越困难,这需要在材料和电路设计方面取得突破。最小化每比特传输的功耗是另一个关键点,尤其是对于人工智能和边缘计算等需要高性能和低能耗的应用而言。此外,确保可扩展性和可制造性以及合理的成本对于广泛应用至关重要。下一代互连的未来需要材料科学家、电气工程师和封装设计师之间的跨学科合作,以创建突破性能、效率和集成度界限的整体解决方案。随着这些技术的进步,它们将继续塑造半导体封装的未来,并在广泛的应用中创造新的可能性。

随着业界致力于开发针对特定应用定制的更高性能、更低功耗的解决方案,预计chiplet的普及将持续下去。下一代封装需要支持异构集成的爆炸式增长,实现互连,以容纳极细间距的 I/O 芯片(间距小于 10 µm)和极细的线/线距(线宽小于 1 µm)电路。总体而言,3D 芯片集集成的目标是实现两个基本性能要求:(1) 更高的效率(以bits/J为单位);(2) 更高的带宽密度(以 IO/mm 或 IO/mm² 为单位)。

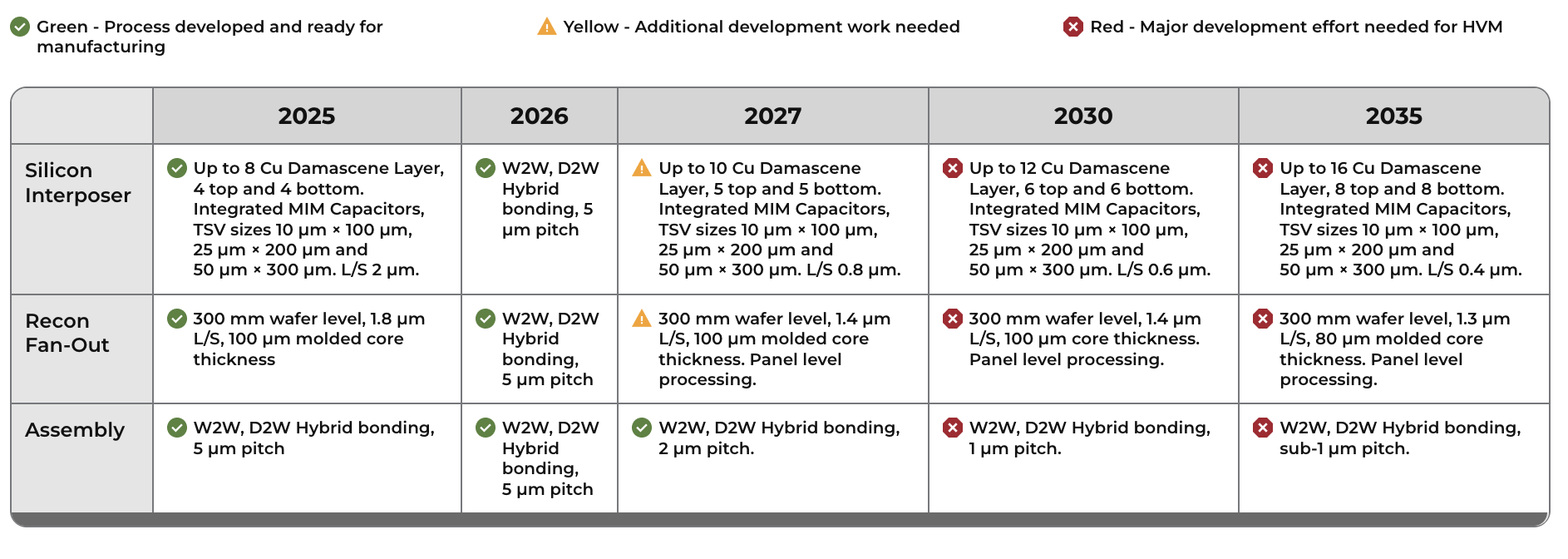

表1:实现未来 HI 的路线图技术发展需求

表1展示了用于互连芯片集并满足未来高性能要求的 HI 路线图。为了满足未来对硅中介层的需求,需要能够在正面生产更多数量的增层,并在背面生产多层 RDL。基板厚度也可能需要从 100 µm 降至 50 µm 或更低。对于重构 fan-out技术,主要的技术驱动力将是实现正面和背面增层 L/S 均小于 1 µm。对于这两种 HI 技术,都需要容纳 I/O 焊盘间距小于 10 µm 的芯片。此时,组装技术将从传统的焊接方法过渡到混合键合。未来的开发工作需要侧重于芯片到晶圆 (D2W) 和芯片到芯片 (D2D) 混合键合,以满足未来的性能和成本目标。